# **Electrical Testing of Passive Components**

Todd L Kolmodin Gardien Services USA Manfred Ludwig Gardien Services China Howard Carpenter Gardien Services USA

## Introduction

Substrates have become more critical with regard to pitch and density in today's designs with challenges for passive components in terms of surface placement. This negates the opportunity for high speed, high cost components to be placed on the surfaces of the PCB. With this the capacitance and resistive components have to be embedded into the design. This has been accomplished with the advent of buried capacitance cores and buried resistors. Unfortunately this has caused some challenges to the ET Test Centers/Labs in the ability to effectively test these buried passive components. Processes have had to change and adapt to these new technologies. The paper will discuss what these new technologies are and how the Electrical Test arena has adapted to provide accurate testing of the buried resistors and accommodate the buried capacitive cores to not receive false errors from the Grid Testers and Flying Probes.

## Resistors

In the past pull-up, terminating and voltage dividing resistors have been placed on the surface of the PCB. Early applications were standard carbon resistors placed on the board utilizing Plated through Holes.

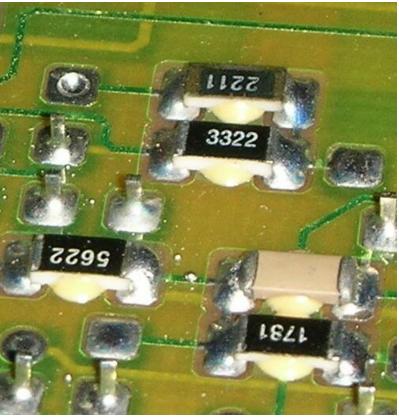

Figure 1: Carbon Resistors (as noted by their color rings)

As can be seen in Figure 1 the standard carbon resistor took up a lot of space on the PCB. You will also notice in the photo that Capacitors are also stealing valuable space from the surface topography. As time progressed SMT Technology was introduced and the older, bulky standard carbon resistor was replaced by the newer SMT packages (Figure 2).

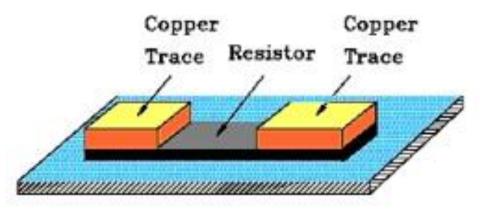

Figure 2: Surface Mount Resistors

This was a very popular innovation to the industry as now the surface footprint was drastically reduced and the topography on the surface of the PCB was now open to accommodate more active components which reduced the overall size of the PCB but also allowed the complexity of the designs to grow. No longer was a PTH as needed for the resistor so this allowed the multilayer to expand its capabilities on the inner layers to provide not only an overall smaller PCB but a more powerful final product.

These technologies albeit reduced the footprint of the PCB but by no means could we have the smartphones and Tablets and many of the day-to-day devices we know and rely on today. Further it would be impossible to use the older technologies of yesteryear to power the mammoth internet infrastructure that we take for granted today. Something still had to change. The next evolution was to hide the passive components completely from the surface of the PCB and allow the needed high power footprints of the BGAs, Micro BGAs and HDI components. As of now these high speed components have challenges to be buried in the board design due to their size and the need for heat dissipation. However the passive components could be. The buried passive component allowed the ability to provide the pull-up, terminating, current limiting and voltage dividing properties without taking needed real-estate from the surfaces of the PCB.

There have been many options of the buried resistor. This spans from the carbon ink screened resistor through to thin film resistor conductor material.

Figure 3: Thin Film Embedded Resistor

This technology allows the ability to develop a buried resistor by the use of a resistive core laminated into the PCB itself. By etching away a "Square" or a multiple of them a specific resistance can be achieved. There is no "hard" component any longer.

## A. Explanation of Ohms-Per-Square

The resistance of a OhmegaPly® resistor:

$$R = R_s \frac{Length \ of \ Resistor}{Width \ of \ Resistor}$$

Equation.1

Where  $R_s$  is the sheet resistance (in ohms per square) of the PRT material. The resistance value of the resistor can be determined by sheet resistance and geometry of the resistor according to the formula above.

Equation.2

Where N is the number of squares (N = L/W)

Figure 4: Thin Film Resistance Calculation

But this now provides a unique challenge to the Electrical Test arena as they need to test this product with the buried signature and also certify the board to the End User specification, be it IPC Class I, II, III or 3/A. Many times these resistors are chained in series or used in parallel and this does not allow the conventional Electrical Test Machine to provide a "Pass." Trying to test these buried resistors by conventional means only results in a "Fail", as usually the resistance is higher than the IPC Class requirement. Further, care has to be maintained to not compromise the resistor itself due to excess current applied.

When we are testing the buried resistor we must take into account the power dissipation of the given resistor. As we know if we apply too much current to a resistor and overload its power dissipation rating, the resistor will burn.

## **Testing Resistors**

Electrical testing is required to validate the correct resistor values and also identify faulty or out-of-tolerance resistors. It is recommended that Electrical test be performed on both the inner layer and the final board so that if a resistor is faulty at the inner layer stage it can be scrapped prior to any further value-add to the PCB. Netlist testing must be used as a learn and compare type of test which cannot validate the expected value. Most of today's CAD/CAM systems have the ability to output tester data with inclusion of the buried passives. The IPC-356A data format provides the inclusion of the buried passives. What must be included are all the resistor locations or test points, the expected value and the upper and lower tolerance values. There are a few different options for testing the resistors. This can be the use of a Universal Grid Tester (Bed-of-Nails), a Flying Probe Tester or the use of a Manual Measurement System. In the end the accuracy of the readings will depend on the accuracy of the metering system being used, the amount of copper between the test probes and the actual resistor, contact resistance and the resistance of the probes and leads. Most important is that the measurement current should not exceed the current carrying capacity of the resistor. This could lead to permanent damage of the resistor.

For most automated test systems the following guidelines should be applied:

- 1. Input the power rating (watts) of the resistor, if this feature is supported by the test system

- 2. Limit the test current used to 20mA

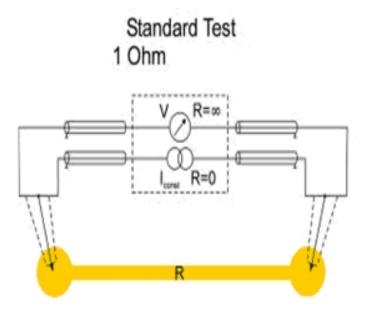

A Flying Probe (or Grid Test) machine basically contains a high speed ohmmeter that allows rapid gathering of resistance values for nets on the PCB.

Figure 5: Resistor Measurement with Current Limiting

Once the resistor value is known the machine will make the necessary tests to the resistors and catalogue the results. It will compare the expected value with the read value (compensating for the allowed tolerances) and internally log the resistor net as Pass or Fail. Once the entire test of the PCB is complete a report ticket will be printed stating the PCB passed or failed and will identify all resistors that failed in addition to the standard Continuity Test results. Many machines of today can also supply a report of all the resistor values read for the given PCB for statistical process monitoring.

### **Protecting the Resistors**

When testing the resistors via a Flying Probe care must be taken to limit the voltage/current drive to the measurement. Flying Probes have two methodologies when taking measurements, Constant Current and Constant Voltage. Depending on the design of the Flying Probe you have could cause some concerns. If the BR record was provided in the raw netlist the machine should make the appropriate determinations of how to best test the resistor. If the system is solely Constant Current source (grid/prober) it should be able to automatically detect if the test parameters are in range. If the system has Constant Voltage capability then it can auto-range itself to the appropriate power level. A Constant Current system is only limited by its internal supply voltage. With a Constant Current secnario the actual power or "Wattage" is not monitored and can be detrimental to the UUT. The Constant Current method is far too restrictive for the range of resistors that are in use today. These measurements should be done in a Constant Voltage mode. In this scenario the current is based on the actual resistance read and not the calculated or anticipated value. In this scenario the resistance is only needed to calculate the required voltage of the source. The measurement parameters are constructed using the E=P/I formula where E =Voltage, P=Power and I = Current. The measurement is taken at the calculated E and the resultant I is measured and calculated in Ohms.

#### **Capacitors**

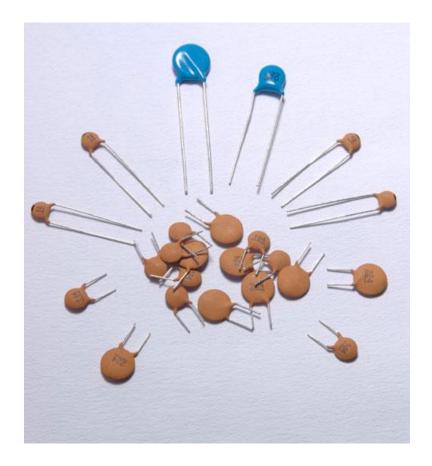

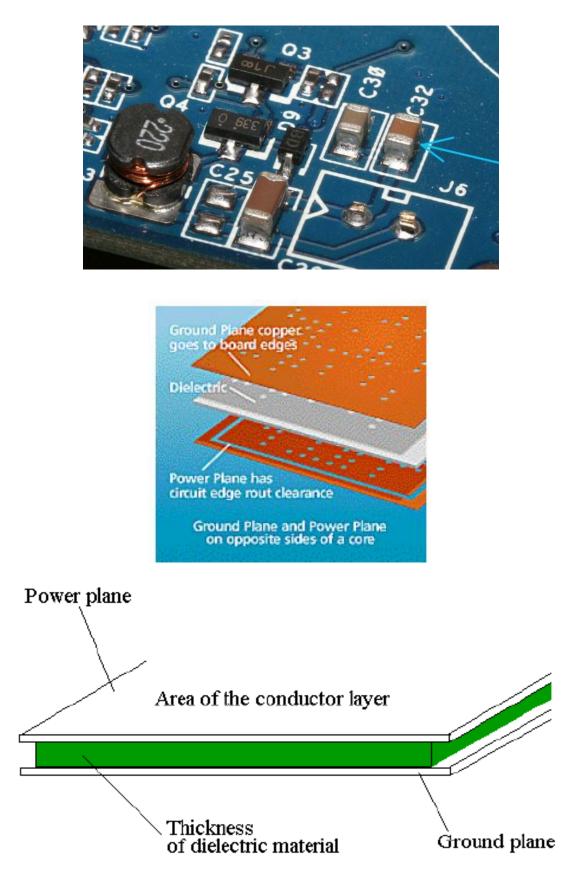

Just as with the buried resistors, capacitance can also be embedded into the PCB. This is done by the use of a capacitive core material laminated into the PCB. This removes the need for surface decoupling capacitors and as with the removal of some of the surface resistors allows more space on the surface of the PCB and allows the overall size to be reduced.

Figure 6: Various Capacitor evolution, ceramic paper, SMT and buried capacitive cores

However this introduces a challenge with Electrical Test. With the buried capacitance in the PCB false "shorts" can be reported by the tester. The standard Electrical Test for shorts applies a voltage (primary point) and reads for current leakage on adjacent nets in the case of the Flying Probe or any nets in the case of the bed-of-nails grid test machine. A specific threshold is set on the machine so that nets to one another must have a minimum resistance between them or a failure is reported. For example, IPC-9252A Class III specifies greater than or equal to 10M Ohms. This measurement is taken very quickly and due to the capacitive charge time the test machine may report this momentary "leak" as a false short.

## Testing

## **Grid Test**

Unfortunately one finds that many of the older Grid Test Machines have no solution for negating this capacitive charge component. Newer machines have the ability to delay the measurement for a specified time to allow for the capacitive charge to stabilize before the reading is taken. This is relatively transparent to the operator. Once the test is initiated the Continuity Test is performed as normal. When the isolation (shorts) test begins the machine applies the test voltage to the PCB and then waits during the input delay time before taking measurements. This allows the capacitive core to charge and stabilize. The end result is a "Pass" rather than a false error reported.

## **Flying Probe**

These machines have the same dilemma when testing PCBs with buried capacitance. Flying Probes do not by default test every net to every net for shorts as the Grid Test machines do. Flying Probes use what is called Adjacency Testing for shorts. One reference probe is set on a net and the other probes measure for leakage in adjacent nets. This window is defined during the CAM process. As with the Grid Test machines the same charge time variable is introduced and can cause false errors to be reported. Earlier software packages driving these machines did not have an accurate way to delay the reading and they were not able to provide a "Pass" to the product which required a manual verification of the error and a human decision made to whether the board was good or not. This was the same with the older Grid Test machines.

Some newer software packages for the Flying Probers did in fact incorporate delay timers to combat the capacitive charge. However these timers were applied to the entire test which would slow the machine down. Although it was a solution it adds time to the overall test on the Flying Probe. Another known software package for the Flying Probe introduced a bit of AI to the test routine which actually monitors for this charging variable. This allows the machine to run at full speed until it detects a possible short. It then falls into a delay routine and takes multiple measurements of the suspect net to determine if it is a capacitive charging variable or an actual short. If the resistance between the two nets charges and a stable resistance reading is obtained within the test parameter threshold the machine will pass the network and move on. If the leakage continues in excess of the timer measurement threshold a true short is indicated and the net will be flagged as a failure. This advantage allows the overall test time of the PCB to remain optimal rather than slowing down every measurement reading resulting in lost velocity and throughput.

## Conclusions

As technology grows and PCB sizes shrink the demand for embedded technologies will only grow. Many end-users are designing embedded passives into their products and the Electrical Test community is expected to provide the test solutions for these new powerful designs. The use of buried resistors is increasing and care must be taken to identify these components during the ET CAM process so that the test machines are aware of them and do not overpower them with standard test parameters. For the design community that uses the buried core technology the manufacturers of this material have always recommended using the largest configuration for the buried resistor as feasible. As noted previously the "square" should be as large as feasible to provide the required resistance while also maintaining the optimum power dissipation level to ensure long life and stability.

Buried capacitance has been around for a long time but is also increasing. The ability for Electrical Test to accurately test this type of product is crucial. Accurately identifying and allowing the buried capacitance component, results in improved throughput and delivery. It also reduces unnecessary delays, troubleshooting and unfortunate scrap of product that is actually good.